# Repetitive short-circuit measurement on Sic Mosfet

Q. Molin<sup>1,a\*</sup>, M. Kanoun<sup>2,b</sup>, C. Raynaud<sup>3,c</sup>, H. Morel<sup>3,d</sup>

<sup>1</sup> Supergrid Institute, 21 rue Cyprian, Villeurbanne 69611 CEDEX, France

<sup>2</sup> EDF R&D, Moret-sur-Loing 77818, France

<sup>3</sup> Univ Lyon, INSA Lyon, CNRS, Ampere, F-69621, France

<sup>a</sup>quentin.molin@supergrid-institute.com, <sup>b</sup>mehdi.kanoun@edf.fr

<sup>c</sup>christophe.raynaud@insa-lyon.fr, <sup>d</sup>herve.morel@insa-lyon.fr

## Abstract

Robustness study for the 1.7 kV SiC MOSFET is presented. After evaluation of the critical energy required for failure, devices were submitted to repetitive short-circuits conditions. Because the power switches experienced very stressful mode, the monitoring of key parameters is required to understand failures which in all occurrence are related to the gate oxide weakness. The strong impact of drain to source bias voltage on the critical energy during short-circuit mode is also investigated. Additionally, test bench and protocols are detailed.

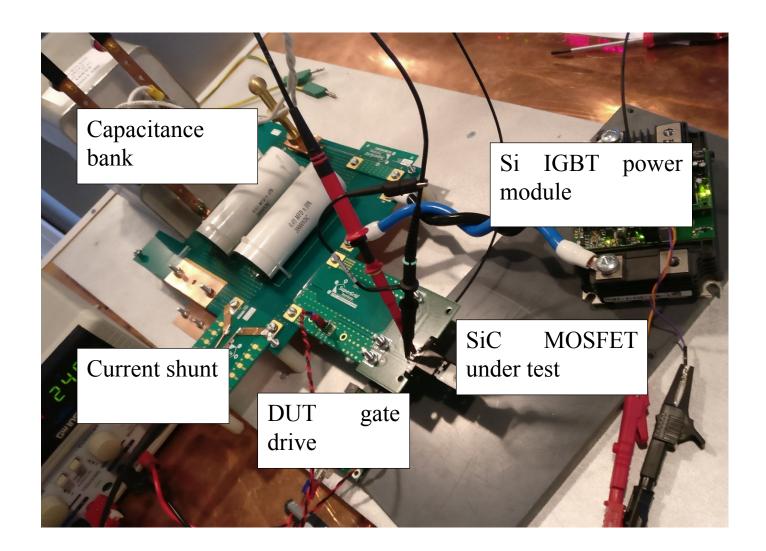

#### Short circuit test bench overall description

- Up to 20 kV short-circuit test

- Devices under test : 1.7 kV 45 m $\Omega$

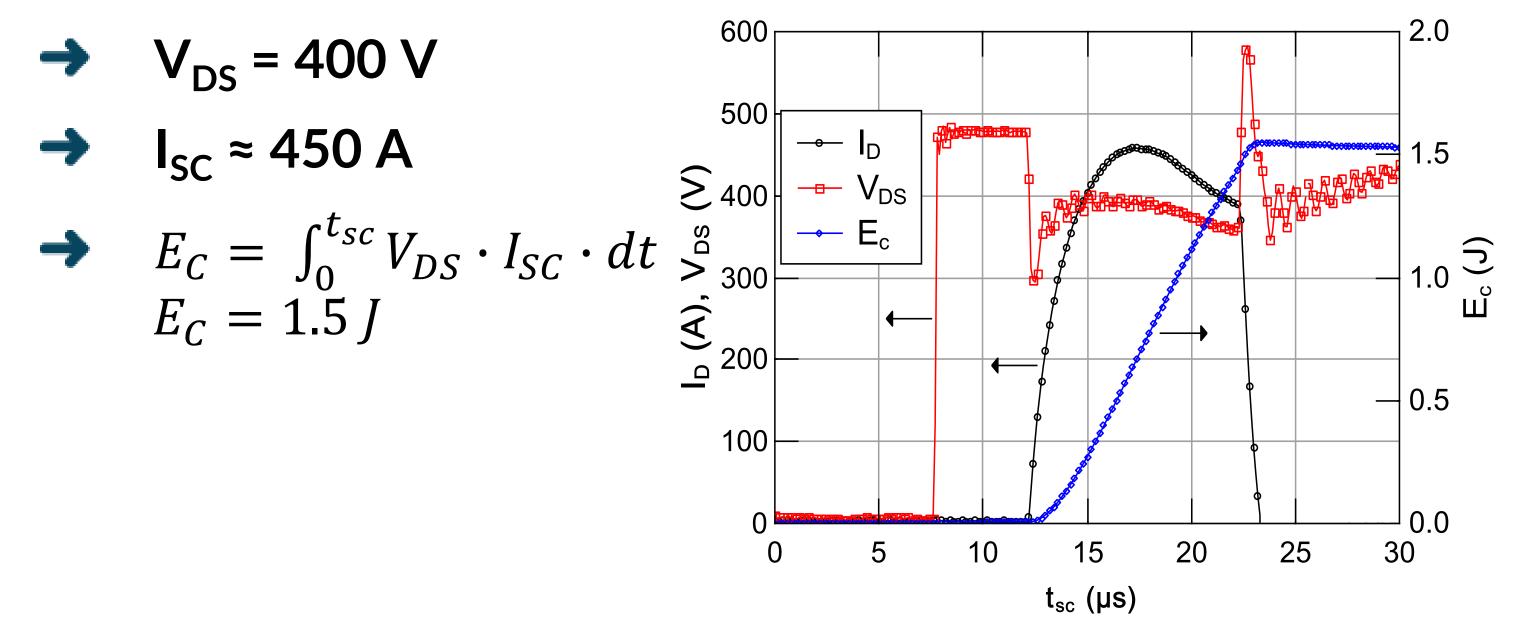

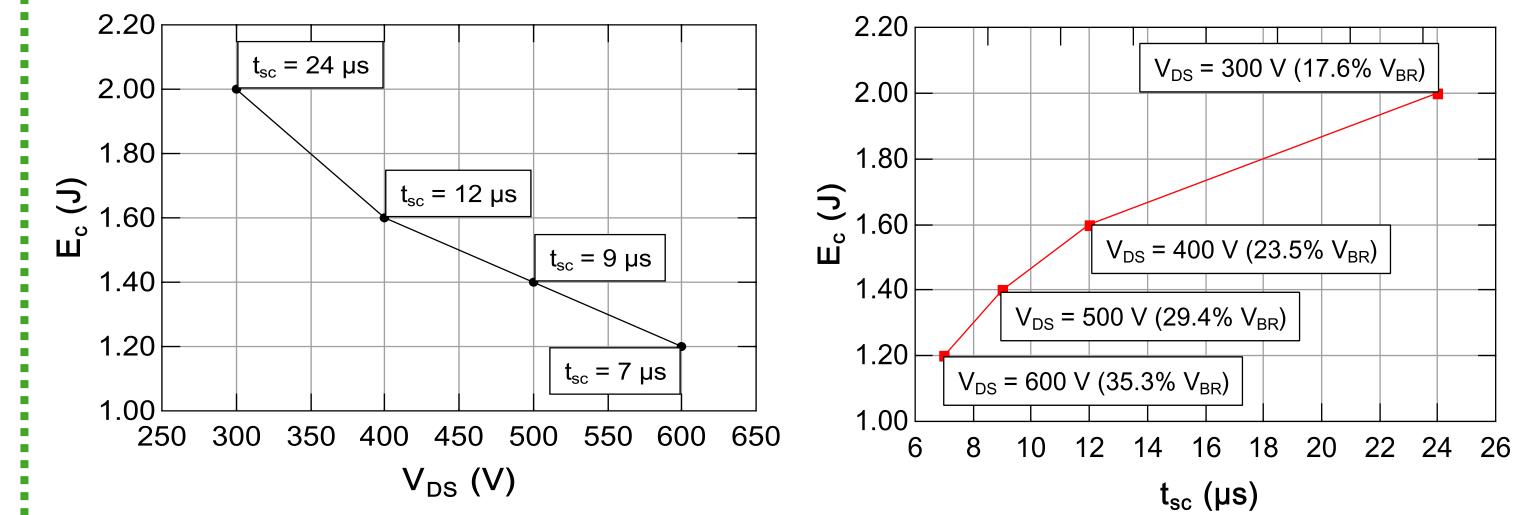

#### **Critical energy estimation**

In order to perform repetitive short-circuit test, the critical  $\rightarrow$ energy needs to be evaluated

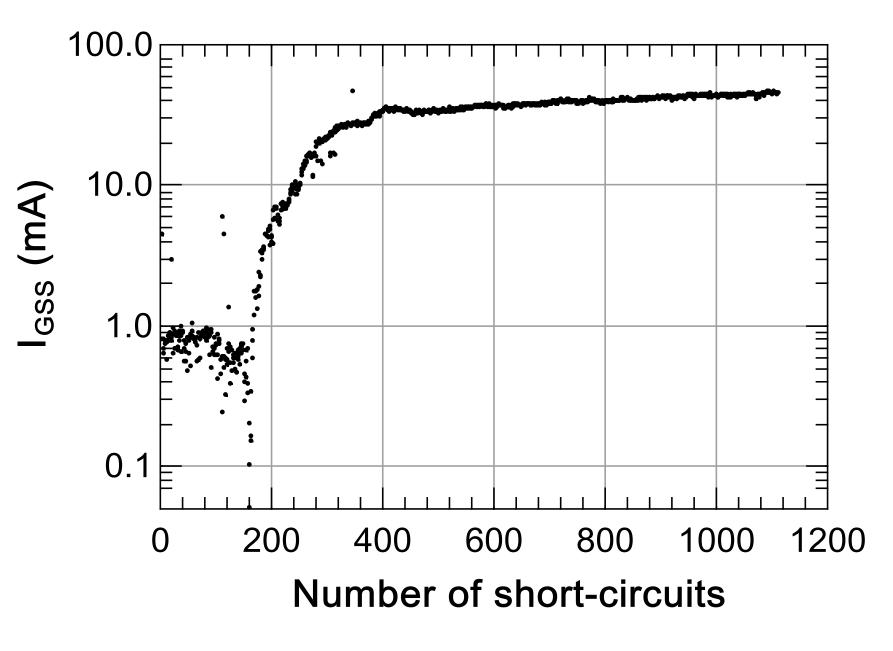

#### Gate leakage current monitoring

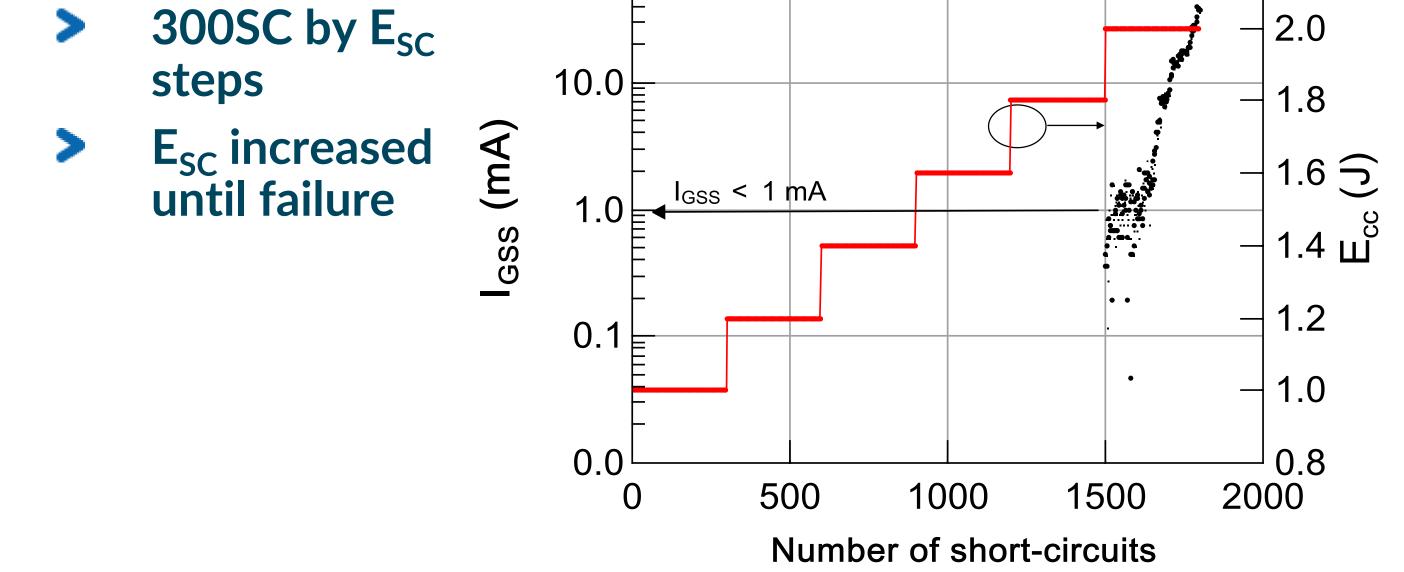

- **I**<sub>GSS</sub> monitoring during RSC

#### Drain to source voltage impact on critical energy

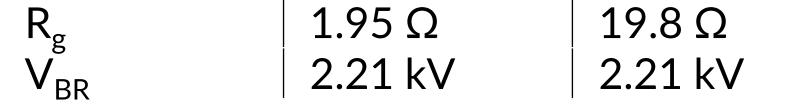

**Test protocol:**

#### First RSC test at 80%.E<sub>C</sub> →

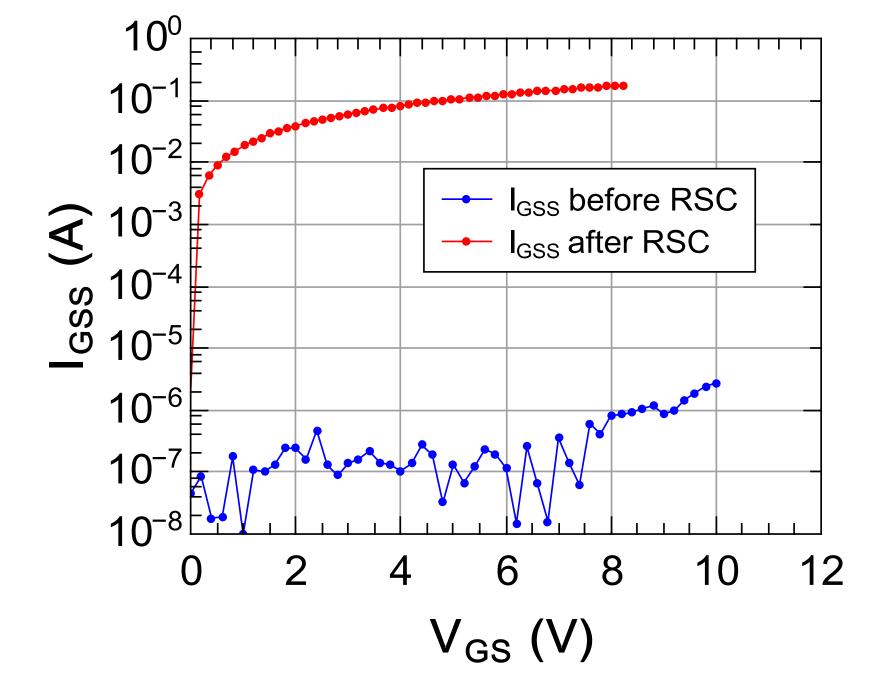

- gate oxyde failure in ~160SC

- Gate leakage current increase show gate degradation

**Key parameters changes**

| Parameters        | Before RSC | After 1000 RSC |

|-------------------|------------|----------------|

| I <sub>GSS</sub>  | 39.4 pA    | >1 mA          |

| V <sub>th</sub>   | 2.86 V     | 2.98 V         |

| R <sub>DSon</sub> | 40 mΩ      | 80.5 mΩ        |

When  $V_{DS}$  is increased then the energy required to → degrade the gate oxide is decreased

Gate leakage current characterization

## Conclusions

- → SiC MOSFET short-circuit withstanding capacity is worrying.

- Once 80%.E<sub>c</sub> of a component is reached, around a few hundred are needed for gate failure

- If the 80%.V<sub>BR</sub> condition is respected for 1.7 kV MOSFET  $\rightarrow$  $t_{sc}$  can be approximated to ~3  $\mu$ s

- There is some critical dispersion on critical energy  $\rightarrow$

- $1,5 J < E_{C} < 2 J$ >

- Strict measurement protocol are needed

SuperGrid Institute, 23 Rue Cyprian, 69100 Villeurbanne - FRANCE