SuperGrid Institute

Your innovation & research partner

DEVELOPING THE ELECTRICITY NETWORKS OF THE FUTURE

The Institute

We are an independent innovation and research company dedicated to the development of technologies for the future system of power transmission.

At a time when it is increasingly important to lower our dependency on fossil fuels and reduce greenhouse gas emissions, we provide our customers and partners with strong technological innovations to accelerate the development of future power grids and the massive integration of renewable energy.

SuperGrid Institute offers

a complete range of technologies and services

Involved in the ecosystem

Because of our important role in building the network of the future, SuperGrid Institute is involved in many international projects, be it as a partner or a leader.

Our expertise, state-of-the-art testing facilities, and ability to innovate and deliver solutions that meet the needs of the market are increasingly recognised.

Our educational mission

To promote understanding of HVDC and MVDC technologies, we engage in education at every level, from secondary-school to life-long learning. Our engineers work alongside PhD students and interns carrying out applied research that addresses industry needs. We also support educational institutions in developing their own training curricula on MVDC, HVDC and supergrid technologies.

SuperGrid Institute at a glance

Our latest news

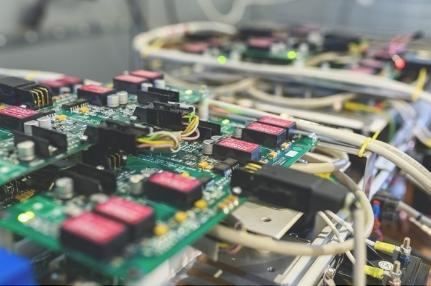

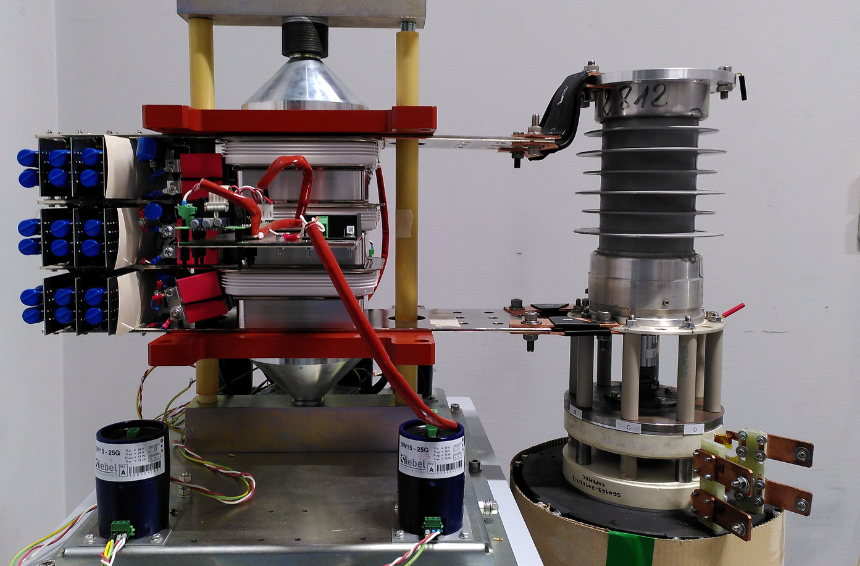

MVDC circuit breaker: introducing our breakthrough HyBreak technology

SuperGrid Institute have developed a MVDC Circuit Breaker which draws on breakthrough HyBreak technology to protect medium-voltage DC grids.

Shaping Europe’s energy future : sharing our strategic vision with the European Commission

Our CTO Bruno Luscan was recently invited to participate in a workshop to discuss the needs and deployment of carbon neutral power systems.

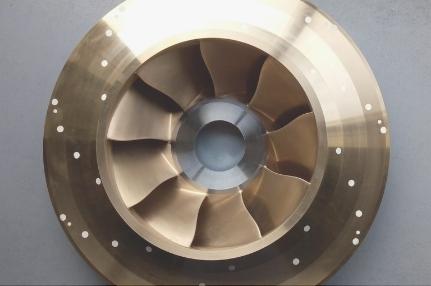

SuperGrid Institute opens the doors to its hydraulic laboratory at the Hydro 21 “RDV Experts” event

The “RDV Experts” are events organised for members of the Hydro 21 association on key themes surrounding the hydraulics ecosystem.